Hello, I've got a guestion.

Let's assume I'm running FV-1 with external clock. Is FV-1 sampling signal with rising or falling clock edge?

FV-1 clock edge

Moderator: frank

Re: FV-1 clock edge

Basically neither or both depending how you look at it. The converters are delta-sigma so they don't really have a clock edge you can reference externally. And even if you could access a clock there is nothing you can really do with it as delta-sigma converters are over sampling converters.

Frank Thomson

Experimental Noize

Experimental Noize

Re: FV-1 clock edge

Well, that complicates things a bit.

But maybe let me explain; I wanted to make pseudo-stereo circuit based on a multiplexer / demultiplexer. External generator produces main clock signal for FV-1 and the second signal, divided by 2 for de/multiplexers, so they're synchronized. And the multiplexer simply switches L/R inputs and outputs. I cannot do it another way bacause I need first DAC to get wet signal and second DAC to get dry signal, to mix it out of FV-1.

I assumed that if the program is executed with every clock tact, I can substitute input signals every other sample.

But maybe let me explain; I wanted to make pseudo-stereo circuit based on a multiplexer / demultiplexer. External generator produces main clock signal for FV-1 and the second signal, divided by 2 for de/multiplexers, so they're synchronized. And the multiplexer simply switches L/R inputs and outputs. I cannot do it another way bacause I need first DAC to get wet signal and second DAC to get dry signal, to mix it out of FV-1.

I assumed that if the program is executed with every clock tact, I can substitute input signals every other sample.

Re: FV-1 clock edge

No way to do this on FV-1. In fact I do not think it is really possible on any device using a delta-sigmal converter. You need a converter like a SAR type converter and I do not think anyone makes one in the audio range anymore, they do not have the performance of a delta-sigma.

If you must run 3 channels of data into the DSP core then you need a processor that can handle 3 or more channels.

If you must run 3 channels of data into the DSP core then you need a processor that can handle 3 or more channels.

Frank Thomson

Experimental Noize

Experimental Noize

Re: FV-1 clock edge

I not sure if you know what I exactly mean.

Anyway, please tell me when the program is execuded? I mean, with rising or falling clock edge?

Anyway, please tell me when the program is execuded? I mean, with rising or falling clock edge?

Re: FV-1 clock edge

UPDATE:

Ok, nevermind. I made some tests with channels multiplexing on prototype and it sucks.

Thank you frank for answers.

Ok, nevermind. I made some tests with channels multiplexing on prototype and it sucks.

Thank you frank for answers.

Re: FV-1 clock edge

I do but delta-sigma converters do not work the way you need a converter to for this. You are assuming there is a sample and hold that occurs each sample period and delta-sigmas do not do that. SAR converters do work that way.

Frank Thomson

Experimental Noize

Experimental Noize

Re: FV-1 clock edge

Yes, but if the program is executed with clock edge, it reads ADC registers in that moment.

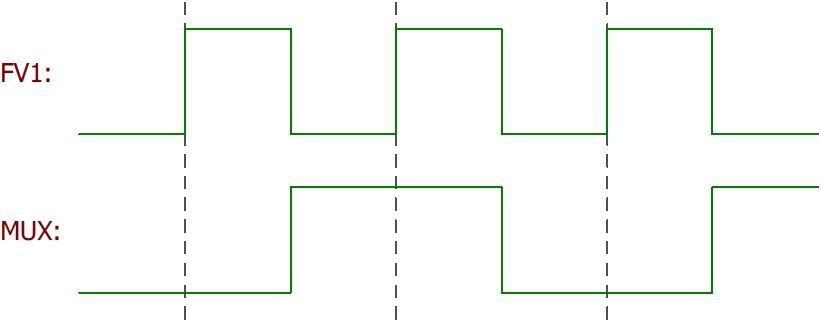

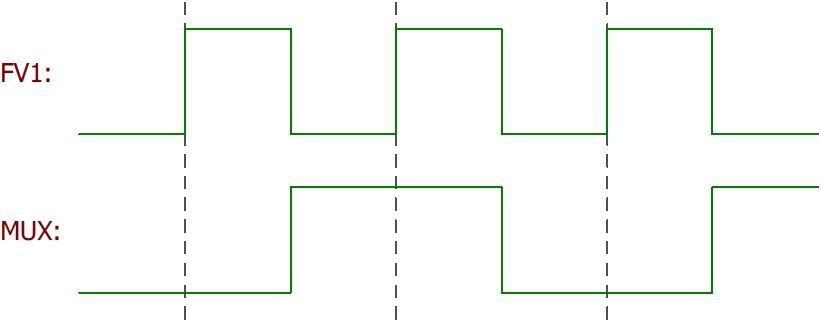

And, if clock signals are synchronized like this:

(assuming it's rising edge in this case) ADC register should have value of left or right channel in reading moment.

Correct me if I'm wrong.

And, if clock signals are synchronized like this:

(assuming it's rising edge in this case) ADC register should have value of left or right channel in reading moment.

Correct me if I'm wrong.

Re: FV-1 clock edge

In a delta-sigma (DS) it is not that simple, while we read a specific register at a specific point in time for the value at that time for the processing core the conversion from analog to digital is far more complex. You are thinking how a SAR converter works by taking a sample at the Fs rate, DS converters sample at a multiple of Fs, 64x or 128x so there is NO WAY to do what you are trying to do by multiplexing an input with a DS based device.

So you are wrong on the conversion part, you are thinking of a SAR and not a DS. FV-1 will NOT work as you want in this case and as far as I know there are no audio range SAR converters, the industry moved to DS as they have better performance. Your only choices are to use a different processor with more inputs and DS converters or a 2 input processor with a SAR converter (if you can find one) but the S/N will suffer since SAR do not have the performance of DS.

So you are wrong on the conversion part, you are thinking of a SAR and not a DS. FV-1 will NOT work as you want in this case and as far as I know there are no audio range SAR converters, the industry moved to DS as they have better performance. Your only choices are to use a different processor with more inputs and DS converters or a 2 input processor with a SAR converter (if you can find one) but the S/N will suffer since SAR do not have the performance of DS.

Frank Thomson

Experimental Noize

Experimental Noize

Re: FV-1 clock edge

Ok, I see now.

Thank you.

Thank you.